### SG6980D

### **FEATURES OVERVIEW**

- Innovative switching-charge multiplier divider

- Multi-vector control for improved PFC output transient response

- 1:2 synchronous switching with SYNC

- Average current mode control

- Remote on/off control

- Power-on sequence control

- Programmable PFC output-voltage control

- Cycle-by-cycle current limiting

- Over-voltage and under-voltage protections

- Brownout and open-loop protections

- Low start-up and operating current

# **APPLICATIONS**

- Active-PFC switching power supplies

- TV and home appliances

- Computer and telecom

# **DESCRIPTION**

The highly integrated SG6980D is designed for power supplies with boost power-factor-correction (PFC). It requires very few external components to achieve desirable operation and includes versatile protection / compensation. It is available in 16-pin DIP and SOP packages. The innovative switching-charge multiplier-divider enhances the PFC circuit's noise immunity. The proprietary multi-vector control scheme provides a fast transient response in a low-bandwidth PFC loop, in which the overshoot and undershoot of the PFC voltage are clamped. If the feedback loop is broken, SG6980D shuts off to prevent extra-high voltage on output. The PFC gate driver can be synchronized with external SYNC signal and the switching noise can be reduced. During start-up, the RDY (ready) is pulled low until the PFC output voltage reaches to the setting level. This signal can be used to control the second forward stage for proper power-on sequence. In addition, SG6980D provides complete protection functions, such as brownout protection and RI open/short.

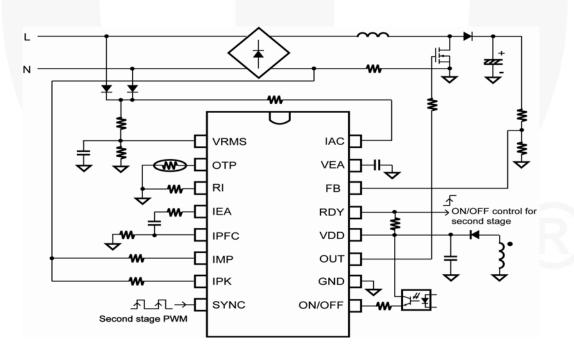

# TYPICAL APPLICATION

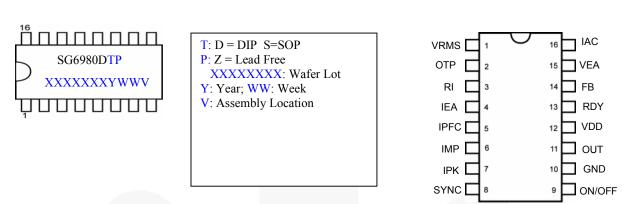

**PIN CONFIGURATION**

# Single-Stage PFC Controller

SG6980D

# **MARKING DIAGRAMS**

# **ORDERING INFORMATION**

| Part Number             | Pb-Free | Package    |  |  |

|-------------------------|---------|------------|--|--|

| SG6980DDZ               |         | 16-Pin DIP |  |  |

| SG6980DSZ (Preliminary) |         | 16-Pin SOP |  |  |

# **PIN DESCRIPTIONS**

| Name   | Pin | Туре                                                                         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|-----|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VRMS   | 1   | Line-Voltage Detection                                                       | Line voltage detection. The pin is used for PFC multiplier and brownout protection. For<br>brownout protection, the controller will be disabled with a 195ms delay time when the VRMS<br>voltage drops below 0.8V. There is a 200mV hysteresis for brownout protection.                                                                                                                                                                                                                  |

| ОТР    | 2   | Over-Temperature<br>Protection                                               | This pin supplies an over temperature protection signal. A constant current is output from this pin. If RI is equal to $24k\Omega$ , then the magnitude of the constant current will be 50uA. An external NTC thermistor must be connected from this pin to ground. The impedance of the NTC thermistor decreases whenever the temperature increases. Once the voltage of the OTP pin drops below 1.2V, the SG6980D will be off, and will auto restart when the voltage is back to 1.4V. |

| RI     | 3   | Oscillator Setting                                                           | The resistance of a resistor connected between RI and ground determines the switching frequency. A resistor with a resistance between $15k\Omega$ and $40K\Omega$ is recommended. The switching frequency is equal to $[1560 / RI]$ kHz, where RI is $k\Omega$ . For example, if RI is equal to $24k\Omega$ , the switching frequency is 65kHz.                                                                                                                                          |

| IEA    | 4   | Current Amplifier Output                                                     | This is the output of the PFC current amplifier. The signal from this pin is compared with an internal sawtooth and determines the pulse width for PFC gate drive.                                                                                                                                                                                                                                                                                                                       |

| IPFC   | 5   | Inverting Input for PFC<br>Current Amplifier                                 | The inverting input of the PFC current amplifier. Proper external compensation circuits result in excellent input power factor via average-current-mode control.                                                                                                                                                                                                                                                                                                                         |

| IMP    | 6   | Non-inverting Input for<br>PFC Current Amplifier<br>and Output of Multiplier | The non-inverting input of the PFC current amplifier and the output of multiplier. Proper<br>external compensation circuits results in excellent input power factor via average current<br>mode control.                                                                                                                                                                                                                                                                                 |

| IPK    | 7   | Peak Current Limit                                                           | The peak current setting for PFC.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SYNC   | 8   | Synchronous Signal                                                           | This pin receives the external switching signal. The PFC switching can be synchronized by SYNC with 1:2 ratio.                                                                                                                                                                                                                                                                                                                                                                           |

| ON/OFF | 9   | Remote On/Off                                                                | Active high. The SG6980D is disabled whenever the voltage at this pin is lower than 1V or the pin is open. When SG6980D is disabled by ON/OFF, the IDD current is lower than $35\mu$ A.                                                                                                                                                                                                                                                                                                  |

| GND    | 10  | Ground                                                                       | The ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| OUT    | 11  | Gate Drive                                                                   | The totem pole output drive for the PFC MOSFET. This pin is internally clamped under 18V to protect the MOSFET.                                                                                                                                                                                                                                                                                                                                                                          |

| VDD    | 12  | Supply                                                                       | The power supply pin. The threshold voltages for start-up and turn-off are 12.5V and 10V, respectively. The operating current is lower than 5mA.                                                                                                                                                                                                                                                                                                                                         |

| RDY    | 13  | Ready Signal Output                                                          | This pin outputs a ready signal to control the power on sequence. Once the SG6980D is turned on and the FB (PFC feedback input) voltage is higher than 2.7V, this pin locks to the high impedance. Disable the SG6980D resets this pin low.                                                                                                                                                                                                                                              |

| FB     | 14  | Feedback Input                                                               | The feedback input for PFC voltage loop. The inverting input of PFC error amp. This pin is connected to the PFC output through a divider network.                                                                                                                                                                                                                                                                                                                                        |

| VEA    | 15  | Error Amplifier Output                                                       | The error amplifier output for PFC voltage feedback loop. A compensation network (usually a capacitor) is connected between this pin and ground. A large capacitor value results in a narrow bandwidth and improves the power factor.                                                                                                                                                                                                                                                    |

| IAC    | 16  | Input AC Current                                                             | This input is used to provide current reference for the multiplier. The suggested maximum $I_{\text{AC}}$ is 350 $\mu\text{A}.$                                                                                                                                                                                                                                                                                                                                                          |

**Product Specification**

SG6980D

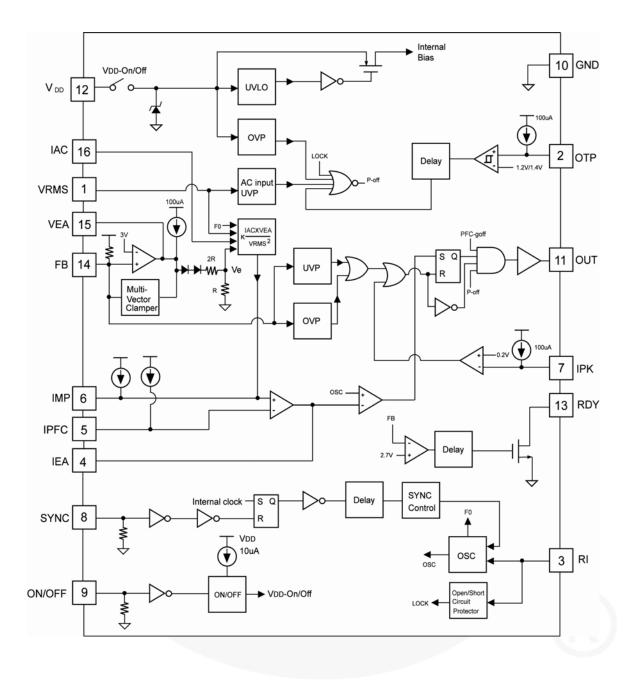

# **BLOCK DIAGRAM**

### SG6980D

# **ABSOLUTE MAXIMUM RATING**

| Symbol               | Parameter                                           | Value       | /alue     |             |

|----------------------|-----------------------------------------------------|-------------|-----------|-------------|

| V <sub>VDD</sub>     | DC Supply Voltage*                                  | 25          |           | v           |

| I <sub>AC</sub>      | Input AC Current                                    | 2           |           | mA          |

| V <sub>High</sub>    | OUT, SYNC, ON/OFF, RDY                              | -0.3 to 25V |           | v           |

| V <sub>Low</sub>     | Others                                              | -0.3 to 7V  |           | v           |

| D                    | Power Dissipation                                   | DIP         | 0.8       | 14/         |

| P <sub>D</sub>       |                                                     | SOP         | 0.4       | W           |

| TJ                   | Operating Junction Temperature                      | +150        | +150      |             |

| T <sub>A</sub>       | Operating Ambient Temperature Range                 | -20~+125    | -20~+125  |             |

| T <sub>STG</sub>     | Storage Temperature RDY                             | -55 to +150 |           | °C          |

| _                    | Thermal Resistance (Junction-to-Case)               | DIP         | 36.70     | °C <i>W</i> |

| R <sub>θj-C</sub>    |                                                     | SOP         | SOP 37.76 |             |

| TL                   | Lead Temperature (Wave Soldering or IR, 10 seconds) | 260         | 260       |             |

| V <sub>ESD,HBM</sub> | ESD Capability, Human Body Model                    | 4           | 4         |             |

| V <sub>ESD,MM</sub>  | ESD Capability, Machine Model                       | 250         | 250       |             |

\*All voltage values, except differential voltages, are given with respect to the network ground terminal.

\*Stress beyond those listed under "ABSOLUTE MAXIMUM RATING" may cause permanent damage to the device.

# **RECOMMENDED OPERATING TEMPERATURE :**

| Symbol         | Parameter                     | Value    | Unit |

|----------------|-------------------------------|----------|------|

| T <sub>A</sub> | Operating Ambient Temperature | -20 ~ 85 | °C   |

\*For proper operation

# SG6980D

# **ELECTRICAL CHARACTERISTICS**

$V_{DD}$ =15V,  $T_A$ =25°C unless otherwise noted.

# **V**<sub>DD</sub> Section

| Symbol                | Parameter                                                     | Test Conditions                                           | Min. | Тур. | Max. | Unit |

|-----------------------|---------------------------------------------------------------|-----------------------------------------------------------|------|------|------|------|

| V <sub>DD-OP</sub>    | Continuously Operating Voltage                                |                                                           |      |      | 20   | V    |

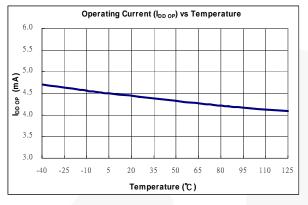

| I <sub>DD-OP</sub>    | Operating Current                                             | RI= 24KΩ,V <sub>DD</sub> = 15V; Gate Open                 |      | 4    | 5    | mA   |

| I <sub>IC-OFF</sub>   | Input Current                                                 | V <sub>ON/OFF</sub> <v<sub>ON, V<sub>DD</sub>=25V</v<sub> |      | 25   | 35   | μA   |

| I <sub>DD-ST</sub>    | Start-up Current                                              | $V_{DD} < V_{DD-ON}$ -0.16V                               |      | 10   | 20   | μA   |

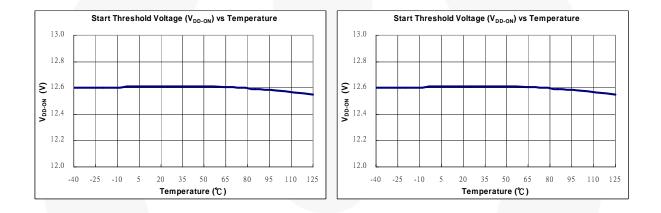

| V <sub>DD-ON</sub>    | Start Threshold Voltage                                       |                                                           | 11.5 | 12.5 | 13.5 | V    |

| V <sub>DD-OFF</sub>   | Minimum Operating Voltage                                     |                                                           | 9    | 10   | 11   | V    |

| V <sub>DD-OVP</sub>   | V <sub>DD</sub> Over-Voltage Protection with<br>Debounce Time |                                                           | 23.5 | 24.5 | 25.5 | V    |

| t <sub>D-VDDOVP</sub> | Debounce Time of V <sub>DD</sub> OVP Protection               |                                                           | 10   |      | 40   | μs   |

# **Oscillator & Green-Mode Operation**

| Symbol              | Parameter                       | Test Conditions | Min. | Тур. | Max. | Unit |

|---------------------|---------------------------------|-----------------|------|------|------|------|

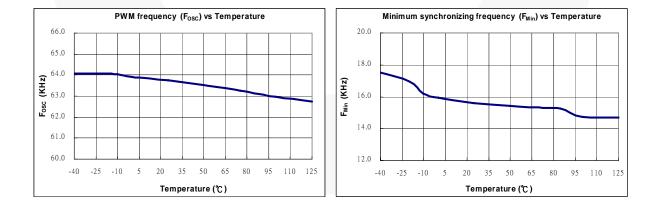

| Fosc                | PWM Frequency                   | RI= 24KΩ        | 62   | 65   | 68   | KHz  |

| RI                  | Nominal RI Value                |                 | 15   |      | 40   | KΩ   |

| RI <sub>OPEN</sub>  | Maximum RI Value for Protection |                 |      | 200  |      | ΚΩ   |

| RI <sub>SHORT</sub> | Maximum RI Value for Protection |                 |      | 2    |      | KΩ   |

# VRMS for UVP and RDY

| Symbol                 | Parameter                                                                 | Test Conditions | Min.                            | Тур.                            | Max.                            | Unit |

|------------------------|---------------------------------------------------------------------------|-----------------|---------------------------------|---------------------------------|---------------------------------|------|

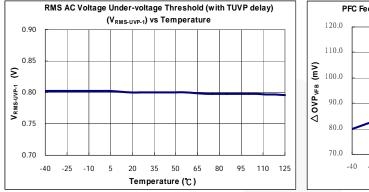

| V <sub>RMS-UVP-1</sub> | RMS AC Voltage Under-voltage Threshold (with $T_{\text{UVP}}$ Delay)      |                 | 0.75                            | 0.80                            | 0.85                            | V    |

| V <sub>RMS-UVP-2</sub> | Recovery Level on VRMS for UVP Mode                                       |                 | V <sub>RMS-UVP-1</sub><br>+0.18 | V <sub>RMS-UVP-1</sub><br>+0.20 | V <sub>RMS-UVP-1</sub><br>+0.22 | V    |

| t <sub>uvp</sub>       | Under-Voltage Protection Propagation<br>Delay Time (No Delay at Start-up) |                 | 150                             | 195                             | 240                             | ms   |

# **Voltage Error Amplifier**

| Symbol               | Parameter                                     | Test Conditions | Min.                        | Тур.                        | Max.                        | Unit  |

|----------------------|-----------------------------------------------|-----------------|-----------------------------|-----------------------------|-----------------------------|-------|

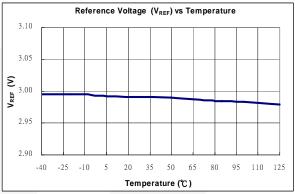

| V <sub>REF</sub>     | Reference Voltage                             |                 | 2.95                        | 3.00                        | 3.05                        | V     |

| Av                   | Open-Loop Gain                                |                 |                             | 60                          |                             | dB    |

| Zo                   | Output Impedance                              |                 |                             | 110                         |                             | ΚΩ    |

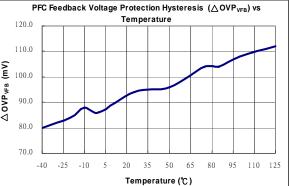

| OVP <sub>FB</sub>    | PFC Over-Voltage Protection on FB             |                 | 1.066 •<br>V <sub>REF</sub> | 1.083 •<br>V <sub>REF</sub> | 1.100 •<br>V <sub>REF</sub> | V     |

|                      | PFC Feedback Voltage Protection<br>Hysteresis |                 | 60                          | 90                          | 120                         | mV    |

| t <sub>ovp-pfc</sub> | Debounce Time of PFC OVP                      |                 | 40                          | 70                          | 120                         | μs    |

| $V_{FB-H}$           | Clamp-High Feedback Voltage                   |                 | 1.033 •<br>V <sub>REF</sub> | 1.050 •<br>V <sub>REF</sub> | 1.066 •<br>V <sub>REF</sub> | V     |

| G <sub>FB-H</sub>    | Clamp-High Gain                               |                 |                             | 500                         |                             | µA/mV |

| V <sub>FB-L</sub>    | Clamp-Low Feedback Voltage                    |                 | 0.916 •<br>V <sub>REF</sub> | 0.950 •<br>V <sub>REF</sub> | 0.966 •<br>V <sub>REF</sub> | V     |

| G <sub>FB-L</sub>    | Clamp-Low Gain                                |                 |                             | 6.5                         |                             | µA/mV |

| I <sub>FB-L</sub>    | Clamp-Low Maximum Current                     |                 | 1.5                         | 2                           |                             | mA    |

| UVP <sub>FB</sub>    | PFC Feedback Under-Voltage Protection         |                 | 0.35                        | 0.40                        | 0.45                        | V     |

| t <sub>UVP-PFC</sub> | Debouce Time of PFC Feedback UVP              |                 | 40                          | 70                          | 120                         | μs    |

# **Current Error Amplifier**

| Symbol                              | Parameter                        | Test Conditions                                      | Min. | Тур. | Max. | Unit |

|-------------------------------------|----------------------------------|------------------------------------------------------|------|------|------|------|

| VOFFSET                             | Input Offset Voltage ((-) > (+)) |                                                      |      | 8    |      | mV   |

| Ai                                  | Open-Loop Gain                   |                                                      |      | 60   |      | dB   |

| BW                                  | Unit Gain Bandwidth              |                                                      |      | 1.5  |      | MHz  |

| CMRR                                | Common-Mode Rejection Ratio      | V <sub>CM</sub> = 0 ~ 1.5V                           |      | 70   |      | dB   |

| V <sub>OUT-HIGH</sub>               | Output High Voltage              |                                                      | 3.2  |      |      | V    |

| V <sub>OUT-LOW</sub>                | Output Low Voltage               |                                                      |      |      | 0.2  | V    |

| I <sub>MR1</sub> , I <sub>MR2</sub> | Reference Current source         | RI=24 KΩ (I <sub>MR</sub> =20+I <sub>RI</sub> • 0.8) | 50   |      | 70   | μA   |

| l                                   | Maximum Source Current           |                                                      | 3    |      |      | mA   |

| I <sub>H</sub>                      | Maximum Sink Current             |                                                      |      | 0.25 |      | mA   |

# **Peak Current Limit**

| Symbol               | Parameter                                                    | Test Conditions         | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------------------------------------------|-------------------------|------|------|------|------|

| l <sub>P</sub>       | Constant Current Output                                      | RI = 24KΩ               | 90   | 100  | 110  | μA   |

| V <sub>PK</sub>      | Peak Current Limit Threshold Voltage                         | V <sub>RMS</sub> =1.05V | 0.15 | 0.20 | 0.25 | V    |

| V PK                 | Cycle-by-Cycle Limit (V <sub>sense</sub> < V <sub>pk</sub> ) | V <sub>RMS</sub> =3V    | 0.35 | 0.40 | 0.45 | V    |

| t <sub>PD-PFC</sub>  | Propagation Delay                                            |                         |      |      | 200  | ns   |

| t <sub>LEB-PFC</sub> | Leading-Edge Blanking Time                                   |                         | 250  | 330  | 430  | ns   |

# **Multiplier**

| Symbol              | Parameter                                            | Test Conditions                                                                   | Min. | Тур. | Max. | Unit |

|---------------------|------------------------------------------------------|-----------------------------------------------------------------------------------|------|------|------|------|

| I <sub>AC</sub>     | Input AC Current                                     | Linear RDY                                                                        | 0    |      | 360  | μA   |

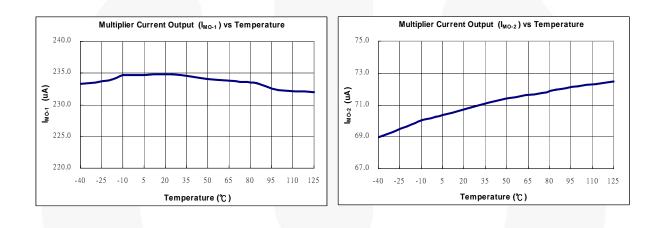

| I <sub>MO-MAX</sub> | Maximum Multiplier Current Output;                   | RI=24 KΩ                                                                          | 230  | 250  |      | μA   |

| I <sub>MO-1</sub>   | Multiplier Current Output<br>(Low-line, High-power)  | V <sub>RMS</sub> =1.05V; I <sub>AC</sub> =90μA;<br>V <sub>EA</sub> =7.5V; RI=24KΩ | 200  | 250  | 280  | μA   |

| I <sub>MO-2</sub>   | Multiplier Current Output<br>(High-line, High-power) | V <sub>RMS</sub> =3V; I <sub>AC</sub> =264μA;<br>V <sub>EA</sub> =7.5V; RI=2 KΩ   | 65   | 85   |      | μA   |

| VIMP                | Voltage of IMP Open                                  |                                                                                   | 3.4  | 3.9  | 4.4  | V    |

# **PFC Output Driver**

| Symbol             | Parameter                      | Test Conditions                                | Min. | Тур. | Max. | Unit |

|--------------------|--------------------------------|------------------------------------------------|------|------|------|------|

| Vz                 | Output Voltage Maximum (clamp) | V <sub>DD</sub> =20V                           |      | 15   | 18   | V    |

| V <sub>OL</sub>    | Output Voltage Low             | V <sub>DD</sub> = 15V; I <sub>O</sub> = 100mA  |      |      | 1.5  | V    |

| V <sub>OH</sub>    | Output Voltage High            | V <sub>DD</sub> = 13V; I <sub>O</sub> = 100mA  | 8    |      |      | V    |

| t <sub>R</sub>     | Rising Time                    | $V_{DD}$ = 15V; $C_L$ = 5nF;<br>OUT = 2V to 9V | 30   | 70   | 120  | ns   |

| t <sub>F</sub>     | Falling Time                   | $V_{DD}$ = 15V; $C_L$ = 5nF;<br>OUT = 9V to 2V | 30   | 50   | 100  | ns   |

| DCY <sub>MAX</sub> | Maximum Duty Cycle             |                                                | 93   |      | 98   | %    |

# **RDY Section**

| Symbol                               | Parameter                                                       | Test Conditions        | Min. | Тур. | Max. | Unit |

|--------------------------------------|-----------------------------------------------------------------|------------------------|------|------|------|------|

| FB <sub>-RDY-high</sub>              | FB Voltage, RDY High Impedance                                  |                        |      | 2.7  | 1    | V    |

| I <sub>FB-RDY-high</sub>             | Input Leakage Current, RDY High<br>Impedance                    | FB=2.5V                |      |      | 500  | nA   |

| V <sub>OL</sub>                      | Output Voltage Low, RDY Failed                                  | I <sub>SINK</sub> =1mA |      |      | 0.5  | V    |

| t <sub>RDY-delay time</sub>          | Interval Between FB > 2.7V and RDY High<br>Impedance            |                        |      | 4    | 6    | ms   |

| $t_{RDY	ext{-}UVP	ext{-}delay}$ time | Delay Time Between Gate off and RDY Pull<br>Low when UVP Occurs |                        | 10   |      | 16   | ms   |

# **OTP Section**

| Symbol               | Parameter              | Test Conditions | Min. | Тур. | Max. | Unit |

|----------------------|------------------------|-----------------|------|------|------|------|

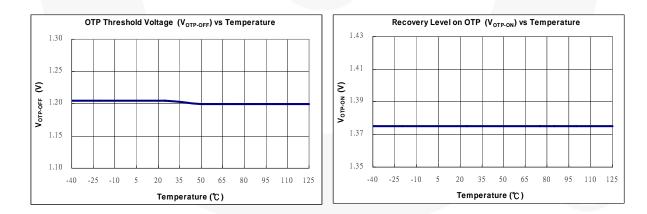

| I <sub>OTP</sub>     | OTP Pin Output Current | RI = 24KΩ       | 90   | 100  | 110  | μA   |

| V <sub>OTP-OFF</sub> | OTP Threshold Voltage  |                 | 1.15 | 1.20 | 1.25 | V    |

| V <sub>OTP-ON</sub>  | Recovery Level on OTP  |                 | 1.35 | 1.40 | 1.45 | V    |

| T <sub>OTP</sub>     | OTP Debounce Time      |                 | 10   |      | 40   | μs   |

# **SYNC Section**

| Symbol                   | Parameter                                                       | Test Conditions | Min.                            | Тур. | Max. | Unit |

|--------------------------|-----------------------------------------------------------------|-----------------|---------------------------------|------|------|------|

| V <sub>SYNC-HIGH</sub>   | Synchronizing Signal High Threshold                             |                 | 3.5                             |      |      | V    |

| V <sub>SYNC-LOW</sub>    | Synchronizing Signal Low Threshold                              |                 |                                 |      | 0.9  | V    |

| F <sub>Min</sub>         | Minimum Synchronizing Frequency                                 | RI=24KΩ         | 2 •<br>(F <sub>osc</sub> -12.5) |      |      | KHz  |

| F <sub>Max</sub>         | Maximum Synchronizing Frequency                                 |                 |                                 |      | 250  | KHz  |

| t <sub>MIN_PULSE_W</sub> | Minimum Synchronizing Pulse Width                               | RI = 24KΩ       | 100                             | 200  | 500  | ns   |

| t <sub>MAX_PULSE_W</sub> | Maximum Synchronizing Pulse Width                               | RI = 24KΩ       |                                 | 15.8 |      | μs   |

| t <sub>D-65KHZ</sub>     | Delay Time Between SYNC and OUT,<br>Switching Frequency = 65KHz | RI=24KΩ         | 1                               |      | 3    | μs   |

| t <sub>D-50KHZ</sub>     | Delay Time Between SYNC and OUT,<br>Switching Frequency = 50KHz | RI=31.2KΩ       | 1                               |      | 3    | μs   |

# **ON/OFF Section**

| Symbol              | Parameter                       | Test Conditions | Min. | Тур. | Max. | Unit |

|---------------------|---------------------------------|-----------------|------|------|------|------|

| R <sub>on/off</sub> | Impedance of ON/OFF Pin         |                 | 18   | 27   | 50   | ΚΩ   |

| V <sub>ON</sub>     | High Threshold of Enable Signal |                 | 3    |      |      | V    |

| V <sub>OFF</sub>    | Low Threshold of Disable Signal |                 |      |      | 1    | V    |

SG6980D

# **TYPICAL CHARACTERISTICS**

# SG6980D

# **OPERATION DESCRIPTION**

The highly integrated SG6980D is designed for a power supply with boost PFC. It requires very few external components to achieve high performance and versatile protections / compensation.

The PFC function is implemented by average current mode control. The patented switching-charge multiplier-divider provides a high-degree of noise immunity for the PFC circuit. This also enables the PFC circuit to operate over a much wider region. The proprietary multi-vector output voltage control scheme provides a fast transient response in a low-bandwidth PFC loop, in which the overshoot and undershoot of the PFC voltage are clamped. If the feedback loop is broken, the SG6980D shuts off the PFC to prevent extra-high voltage on output. Programmable two-level high/low line compensation optimizes THD performance.

In addition, SG6980D provides complete protection functions, such as brownout protection and RI open/short.

### **Switching Frequency and Current**

#### Sources

The switching frequency of SG6980D can be programmed by the resistor  $R_1$  connected between RI pin and GND. The relationship is:

For example, a  $24k\Omega$  resistor R<sub>I</sub> results in a 65kHz switching frequency. Accordingly, constant current I<sub>T</sub> flows through R<sub>I</sub>:

$$I_{T} = \frac{1.2V}{R_{I} (k\Omega)} (mA) \dots (2)$$

I<sub>T</sub> is used to generate internal current reference.

If there is a SYNC signal input, the switching frequency is defined by the SYNC signal. The SNYC frequency must be larger than the programmed switching frequency, less 6KHz.

### Line Voltage Detection (V<sub>RMS</sub>)

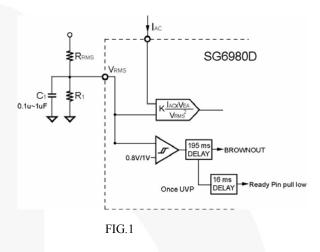

Figure 1 shows a resistive divider with low-pass filtering for line-voltage detection on VRMS pin. The  $V_{RMS}$  voltage is used for the PFC multiplier, brownout protection, and RDY control.

For brownout protection, the SG6980D is disabled with a 195ms delay time if the voltage  $V_{RMS}$  drops below 0.8V.

For PFC multiplier and RDY control, please refer to below sections for more detail.

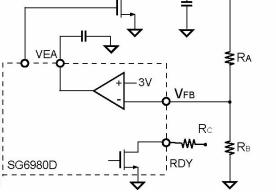

# **PFC Output Voltage Control**

For a universal input (90VAC  $\sim$  264VAC) power supply applying active boost PFC and forward as a second stage, the output voltage of PFC is usually designed around 400V.

FIG.2 Output Voltage Setting

### **ON/OFF**

For ON/OFF control, the SG6980D is disabled immediately if the voltage at this pin is below 1V. Usually, the pin opens when turn off can have the best power saving. The operating current during turn off is less than  $35\mu$ A.

# **SYNC Signal Section**

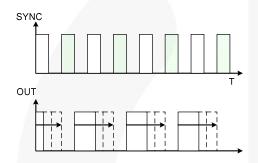

The SG6980D can synchronize half frequency of the SYNC signal and the synchronize signal provided by second stage. This reduces switching noise and the ripple on the output voltage. Figure 3 shows the relationship between the OUT and SYNC signals.

FIG.3 Synchronized Interleaving-Switching

# **RDY Signal Section**

SG6980D provides a RDY pin to inform the next stage and other applications. RDY signal is high impedance when the FB voltage goes up to 2.7V and the delay around 5ms. Use the pin to turn on the second stage PWM when the bulk capacitor voltage is high enough. The RDY pin (open-drain structure) is used for the next-stage-ready signal.

# **PFC Operation**

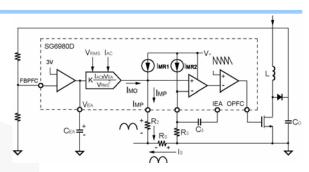

The purpose of a boost active power factor corrector (PFC) is to shape the input current of a power supply. The input current waveform and phase follow that of the input voltage. Using SG6980D, average-current-mode control is utilized for continuous current mode for the PFC booster. With the innovative multi-vector control for voltage loop and switching-charge multiplier/divider for current reference, excellent input power factor is achieved with good noise immunity and transient response. Figure 4 shows the total control loop for the average-current-mode control circuit of SG6980D.

FIG.4 Multiplier and Control Loop of PFC Stage

The current source output from the switching-charge multiplier/divider can be expressed as:

$$MO = K \times \frac{I_{AC} \times V_{EA}}{V_{RMS}^{2}} (\mu A)$$

(4)

$I_{IMP}$ , the current output from IMP pin, is the summation of  $I_{MO}$  and  $I_{MR1}$ .  $I_{MR1}$  and  $I_{MR2}$  are identical fixed current sources.  $R_2$  and  $R_3$  are also identical. They are used to pull high the operating point of the IMP and ICS pins if the voltage across  $R_S$  goes negative with respect to ground.

Through the differential amplification of the signal across  $R_s$ , better noise immunity is achieved. The output of IEA is compared with an internal sawtooth and the pulse width for PFC is determined. Through the average current-mode control loop, the input current  $I_s$  is proportional to  $I_{MO}$ .

$$I_{MO} \times R_2 = I_S \times R_S$$

(5)

According to Equation 5, the minimum value of R2 and maximum of  $R_s$  can be determined because  $I_{MO}$  should not exceed the specified maximum value.

There are different concerns in determining the value of the sense resistor  $R_s$ . The value of  $R_s$  should be small enough to reduce power consumption, but large enough to maintain the resolution. A current transformer (CT) may be used to improve the efficiency of high-power converters.

To achieve a good power factor, the voltage for V<sub>RMS</sub> and V<sub>EA</sub> should be kept as DC as possible according to Equation 4. Good RC filtering for V<sub>RMS</sub> and narrow bandwidth (lower than the line frequency) for voltage loop are suggested for better input current shaping. The transconductance error amplifier has output impedance R<sub>o</sub> and a capacitor C<sub>EA</sub> (1 $\mu$ F ~ 10 $\mu$ F) connected to ground (as shown in FIG. 4). This establishes a dominant pole *f1* (Equation 6) for the voltage loop.

### SG6980D

#### Single-Stage PFC Controller

$$f_1 = \frac{1}{2\pi \times R_0 \times C_{EA}}$$

(6)

The average total input power can be expressed as:

$\begin{aligned} & \mathsf{Pin} = \mathsf{Vin}(\mathsf{rms}) \times \mathsf{lin}(\mathsf{rms}) \\ & \propto \mathsf{V}_{\mathsf{RMS}} \times \frac{\mathsf{I}_{\mathsf{AC}} \times \mathsf{V}_{\mathsf{EA}}}{\mathsf{V}_{\mathsf{RMS}}^2} \\ & \propto \mathsf{V}_{\mathsf{RMS}} \times \frac{\frac{\mathsf{Vin}}{\mathsf{V}_{\mathsf{RMS}}^2} \times \mathsf{V}_{\mathsf{EA}}}{\mathsf{V}_{\mathsf{RMS}}^2} \propto \mathsf{V}_{\mathsf{EA}} \end{aligned}$

From Equation 7,  $V_{EA}$ , the output of the voltage error amplifier, controls the total input power and the power delivered to the load.

### **Multi-Vector Error Amplifier**

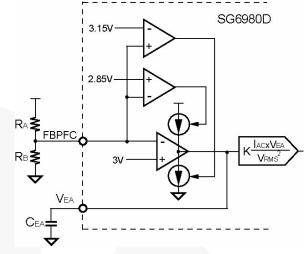

The voltage-loop error amplifier is transconductance, which has high output impedance (>  $90k\Omega$ ). A capacitor  $C_{EA}$  (1 $\mu$ F ~ 10 $\mu$ F) connected from VEA to ground provides a dominant pole for the voltage loop. Although the PFC stage has a low bandwidth voltage loop for better input power factor, the innovative multi-vector error amplifier provides a fast transient response to clamp the overshoot and undershoot of the PFC output voltage. Figure 5 shows the voltage loop with multi-vector for fast transient error amplifier. When the variation of the feedback voltage exceeds  $\pm$  5% of the reference voltage, the transconductance error amplifier adjusts its output impedance to increase the loop response. If the feedback resistance is opened, SG6980D shuts off immediately to prevent extra-high voltage on the output capacitor.

FIG. 5 Voltage Error Amplifier with Multi-Vector

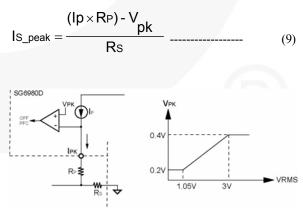

# **Cycle-by-Cycle Current Limiting**

SG6980D provides cycle-by-cycle current limiting for PFC stages. Figure 6 shows the peak current limit for the PFC stage. The PFC gate drive is terminated once the voltage on IPK pin goes below  $V_{PK}$ .

The voltage of  $V_{RMS}$  determines the voltage of  $V_{PK}$ . The relationship between  $V_{PK}$  and  $V_{RMS}$  is shown in Figure 6.

The amplitude of the constant current  $I_P$  is determined by the internal current reference  $I_T$ , according to the following equation:

$$|p = 2 \times I_T = 2 \times \frac{1.2V}{R_I}$$

(8)

Therefore the peak current of the I<sub>s</sub> is given by:

© System General Corp. Version 1.0.1 (IAO33.0071.B0 www.sg.com.tw • www.fairchildsemi.com September 17, 2007

### **Gate Drivers**

SG6980D output stages are fast totem-pole gate drivers. The output driver is clamped by an internal 18V Zener diode to protect the power MOSFET.

# **Over-Temperature Protection**

SG6980D provides an OTP pin for over-temperature protection. A constant current is output from this pin. If RI is equal to  $24k\Omega$ , the magnitude of the constant current is  $50\mu$ A. An external NTC thermistor must be connected from this pin to ground. When the OTP voltage drops below 1.2V, SG6980D shuts down. SG6980D auto restarts when the OTP voltage is higher than 1.4V.

# **Protections & Built-in Latch Circuit**

The SG6980D provides full protection functions to prevent the power supply and the load from being damaged. The protection features include:

*PFC Feedback Over-Voltage Protection.* When the PFC feedback voltage exceeds the over-voltage threshold, the SG6980D inhibits the PFC switching signal. This protection prevents the PFC power converter from operating abnormally while the FB pin is open.

*PFC Feedback Under-Voltage Protection.* The SG6980D stops the PFC switching signal whenever the PFC feedback voltage drops below the under-voltage threshold. This protection feature is designed to prevent the PFC power converter from experiencing abnormal conditions while the FB pin is shorted to ground.

VDD Over-Voltage Protection. The built-in clamping circuit clamps  $V_{DD}$  whenever the  $V_{DD}$  voltage exceeds the over-voltage threshold.

*RI Pin Open / Short Protection.* The RI pin is used to set the switching frequency and internal current reference. If the RI pin is shorted or open, SG6980D turns off.

# Product Specification

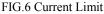

# **PCB Layout**

The SG6980D has a single ground pin. High sink currents in the output cannot be returned separately. Good high-frequency or RF layout practices should be followed. Avoid long PCB traces and component leads. Locate decoupling capacitors near the SG6980D. A resistor of  $5 \sim$  $20\Omega$  is recommended for connecting in series from the output to the gate of the MOSFET.

Isolating the interference between the PFC and PWM stages is also important. Figure 7 shows an example of the PCB layout. The *ground trace 1* is connected from the ground pin of SG6980D to the decoupling capacitor, which should be low impedance and as short as possible. The *ground trace 2* provides a signal ground. It should be connected directly to the decoupling capacitor  $C_{DD}$  and/or to the ground pin of the SG6980D. The *ground trace 3* is independently tied from the decoupling capacitor to the PFC output capacitor  $C_0$ . The ground in the output capacitor  $C_0$  is the major ground reference for power switching. To provide a good ground reference and reduce the switching noise of both the PFC and PWM stages, the *ground traces 6 and 7* should be located very near and be low impedance.

The ICS pin is connected directly to  $R_S$  through  $R_3$  to improve noise immunity. (Beware that it may incorrectly be connected to the ground trace 2). The IMP and IPK pins should be connected directly via the resistors  $R_2$  and  $R_P$  to another terminal of  $R_S$ .

FIG. 7 PCB Layout

SG6980D

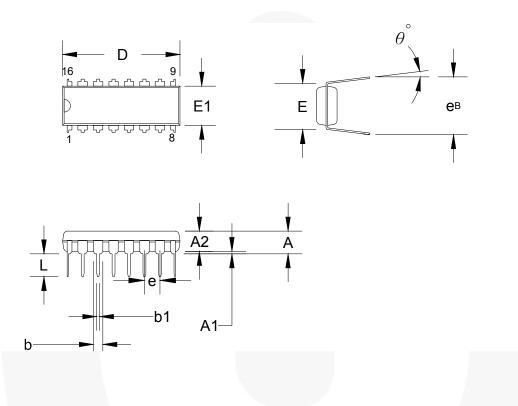

# PACKAGE INFORMATION 16 PINS – PLASTIC DIP (D)

# **Dimensions:**

| Symbol         | Millimeter |        |                 | Inch  |       |                 |  |

|----------------|------------|--------|-----------------|-------|-------|-----------------|--|

| Symbol         | Min.       | Тур.   | Max.            | Min.  | Тур.  | Max.            |  |

| A              |            |        | 5.334           |       |       | 0.210           |  |

| A1             | 0.381      |        |                 | 0.015 |       |                 |  |

| A2             | 3.175      | 3.302  | 3.429           | 0.125 | 0.130 | 0.135           |  |

| b              |            | 1.524  |                 |       | 0.060 |                 |  |

| b1             |            | 0.457  |                 |       | 0.018 |                 |  |

| D              | 18.669     | 19.177 | 19.685          | 0.735 | 0.755 | 0.775           |  |

| Е              |            | 7.620  |                 |       | 0.300 |                 |  |

| E1             | 6.121      | 6.299  | 6.477           | 0.241 | 0.248 | 0.255           |  |

| е              |            | 2.540  |                 |       | 0.100 |                 |  |

| L              | 2.921      | 3.302  | 3.810           | 0.115 | 0.130 | 0.150           |  |

| e <sub>B</sub> | 8.509      | 9.017  | 9.525           | 0.335 | 0.355 | 0.375           |  |

| θ              | 0°         | 7°     | 15 <sup>°</sup> | 0°    | 7°    | 15 <sup>°</sup> |  |

SG6980D

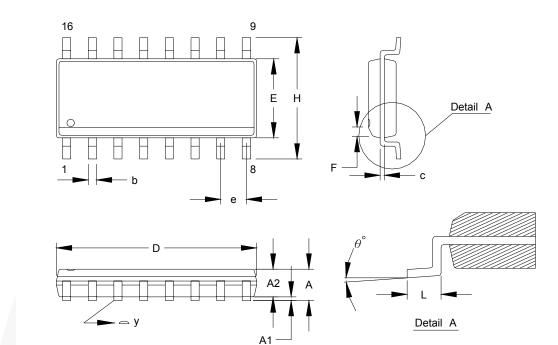

# 16 PINS - PLASTIC SOP (S)

# **Dimension:**

| Symbol | Millimeter | Millimeter |        |       | Inch      |       |  |  |

|--------|------------|------------|--------|-------|-----------|-------|--|--|

| Symbol | Min.       | Тур.       | Max.   | Min.  | Тур.      | Max.  |  |  |

| А      | 1.346      |            | 1.753  | 0.053 |           | 0.069 |  |  |

| A1     | 0.101      |            | 0.254  | 0.004 |           | 0.010 |  |  |

| A2     | 1.244      |            | 1.499  | 0.049 |           | 0.059 |  |  |

| b      |            | 0.406      |        |       | 0.016     |       |  |  |

| С      |            | 0.203      |        |       | 0.008     |       |  |  |

| D      | 9.804      |            | 10.008 | 0.386 |           | 0.394 |  |  |

| Е      | 3.810      |            | 3.988  | 0.150 |           | 0.157 |  |  |

| е      |            | 1.270      |        |       | 0.050     |       |  |  |

| Н      | 5.791      |            | 6.198  | 0.228 |           | 0.244 |  |  |

| L      | 0.406      |            | 1.270  | 0.016 |           | 0.050 |  |  |

| F      |            | 0.381X45°  |        |       | 0.015X45° |       |  |  |

| у      |            |            | 0.101  |       |           | 0.004 |  |  |

| θ°     | 0°         |            | 8°     | 0°    |           | 8°    |  |  |

- 17 -

### SG6980D

### FAIRCHIL

SEMICONDUCTOR

#### TRADEMARKS

The following are registered and unregistered trademarks and service marks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

ACEX® Build it Now™ CorePLUS™ CROSSVOLT™ CTL ™ Current Transfer Logic™ EcoSPARK<sup>®</sup>

# F

Ēairchild<sup>®</sup> Fairchild Semiconductor® FACT Quiet Series™ FACT<sup>®</sup> FAST® FastvCore™ FPS™ FRFET® Global Power Resource<sup>sa</sup> Green FPS™ Green FPS™e-Series™ GTO™ і-Lо™ IntelliMAX™ ISOPLANAR™ MegaBuck™ MICROCOUPLER™ MicroFET™ MicroPak™ MillerDrive™ Motion-SPM™ OPTOLOGIC<sup>®</sup> OPTOPLANAR<sup>®</sup> PDP-SPM™ Power220<sup>®</sup>

Power247® POWEREDGE<sup>®</sup> Power-SPM™ PowerTrench<sup>®</sup> Programmable Active Droop™ QFĔT<sup>®</sup> QS™ QT Optoelectronics™ Quiet Series™ RapidConfigure™ SMART START™ SPM<sup>®</sup> STEALTH™ SuperFET™ SuperSOT™-3 SuperSOT™-6

#### SuperSOT™-8 SvncFET™ The Power Franchise®

p franchise TinyBoost™ TinyBuck™ TinyLogic<sup>®</sup> TINYOPTO™ TinyPower™ TinyPWM™ TinyWire™ µSerDes™ UHC® UniFET™ VСХ™

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS. HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

PRODUCT STATUS DEFINITIONS

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein

- (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- Life support devices or systems are devices or systems

A critical component in any component of a life support, which. (a) are intended for surgical implant into the body or

A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness

#### Definition of Terms Datasheet Identification **Product Status** Definition Advance Information This datasheet contains the design specifications for product Formative or In Design development. Specifications may change in any manner without notice. This datasheet contains preliminary data; supplementary data will be Preliminary First Production published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design No Identification Needed Full Production This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design Obsolete Not In Production This datasheet contains specifications on a product that has been discontinued by Fairchild Semiconductor. The datasheet is printed for reference information only. Rev 131

© System General Corp. Version 1.0.1 (IAO33.0071.B0